# アディティブ法ビルドアップ配線板

電子電装開発センタ 竹 中 尚 一\*1・伊 藤 彰 二\*1・橋 場 浩 樹\*1 電子デバイス研究所 本 戸 孝 治\*2・中 尾 知\*3

Additive Technique for Build-Up Printed Wiring Board with Fine Pattern

Dr. S. Takenaka, S. Ito, H. Hashiba, T. Hondo & O. Nakao

ファイン回路パターンを有するビルドアッププリント配線板の開発をアディティブ法で行った.アディティブ法はサブトラクティブ法よりもファインパターンの形成には有効な手法であった.このような技術は,今後ますます加速する電子機器の高機能化,高密度化に対応した実装回路を提供する多層プリント配線板への応用が期待できる.

We have developed a build-up printed wiring board with fine pattern by using additive technique. Additive technique was more effective than subtractive one in forming fine pattern. The present technique can be applied to fabrication of a future multilayer printed wiring board that provides small-scale electronic devices with high-density wiring space.

#### 1.まえがき

近年,携帯電話やノートブック型パソコンに代表される電子機器の小型・軽量化,多機能化は急速に進展している.これらの電子機器において,各種電子部品間の配線距離はできる限り短くすることが望まれるため,電子部品を実装するプリント配線板は高密度配線,高多層化の方向に進んでいる.このような傾向にともない多層プリント配線板の作製方法も大きく変遷している.

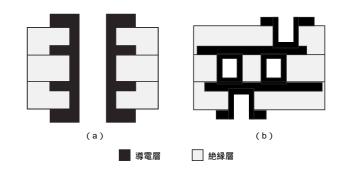

従来の多層プリント配線板はめっきスルーホール法により作製されてきた.これは,絶縁層に導体回路パターンを形成したものを積層した後,全層貫通穴(スルーホール)を開口,スルーホール内部にめっきをほどこってとにより層間の電気的な導通を確保するものである(図1(a)).この手法で作製した配線板ではスルーホール分の配線は一直線上に制限されるため,配線の自由度は低くなる.また,デッドスペースが大きく,スルーホール上には電子部品を実装できないことから高密度配線にはルドアップ法が開発された.これは,絶縁材料とめった問題を解決する手法としてきたいっプ法が開発された.これは,絶縁材料とめっきを組み合わせ,導電層と絶縁層を交互に一層ずつ積層でプリント配線板は各層の任意の位置で層間の電気的導通をと

ることができるため配線の自由度は高くなる.また,表層面の部品実装スペースが大きくなることから高密度配線が可能である.この手法の応用として,めっきによる接続の代わりに導電性ペーストを用いる方法<sup>1,2)</sup>,導電性ペーストを用いて一括積層で行う方法<sup>3,4)</sup>が開発されている.

#### 2. めっきによるビルドアップ法

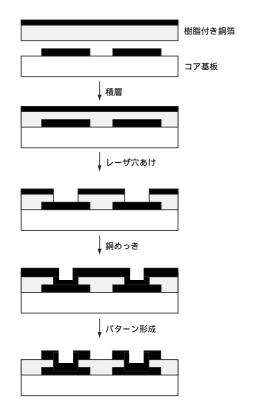

図2に樹脂付き銅箔を用いたビルドアップ法のプロセスを示す.コア基板に樹脂付き銅箔を積層,レーザによるビアホール形成,デスミアの工程を経てめっきを行う. 回路パターン形成法については後述するが,銅箔付き樹

図1 多層プリント配線板の断面図 (a) めっきスルーホール法(b) ビルドアップ法 Structure of multilayer printed wiring boards produced by (a) through hole plating process and (b) build-up process

<sup>\*1</sup> 回路技術開発部

<sup>\*2</sup> マイクロデバイス開発部

<sup>\*3</sup> マイクロデバイス開発部グループ長

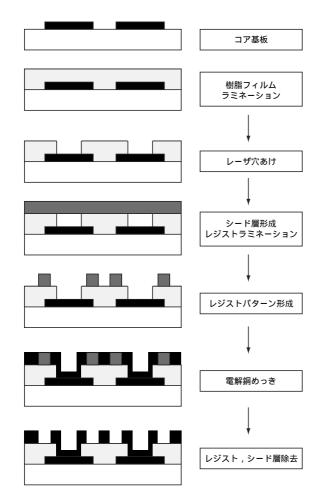

**図2** 樹脂付き銅箔を用いたビルドアップ法のプロセス Process flow of build-up with resin-coated copper foil

脂を用いる場合はサブトラクティブ法で行う.サブトラクティブ法ではレジスト越しに銅箔をエッチングして回路パターンを形成する.樹脂付き銅箔を用いるビルドアップ法では銅箔上にさらに銅めっきをほどこすため銅箔が厚くなる.銅箔が厚くなるとパターン形成における銅箔のエッチング量が多くなるため,ファインパターンの形成は困難となる.

図3に樹脂フィルムを用いたビルドアップ法のプロセスを示す・樹脂フィルムをラミネートした後,めっきをほどこしてパターンを形成するため,めっきの厚さがそのまま銅箔の厚さとなる・よって,めっき条件を制御することにより銅箔を薄くすることで,サブトラクティブ法によるファイン回路パターン形成にある程度対応することができる・しかし,銅箔が薄いパターンは電気抵抗が高くなるといった問題が浮上する・

## 3. サプトラクティブ法とアディティブ法

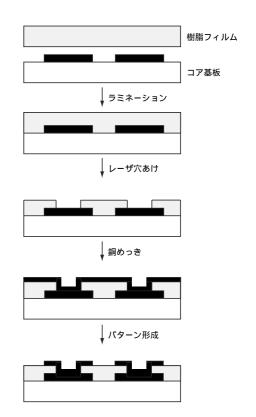

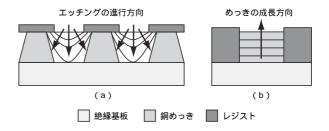

導体回路パターンの形成方法としてサブトラクティブ 法とアディティブ法がある・サブトラクティブ法は全面 にパネルめっきをほどこした後,エッチングレジスト越 しに銅をエッチングすることによりパターンを形成する ものである・しかし,エッチングはレジストに対して垂直方向だけではなく水平方向にも進行するため,レジストに忠実なパターンを形成することは困難である(図4(a))・このようなアンダーカットが発生するため,サブトラクティブ法によるファインパターン形成には限界がある・

図3 樹脂フィルムラミネーションによる ビルドアップ法のプロセス Process flow of build-up with resin film

図4 回路パターン形成法

(a) サプトラクティブ法(b) アディティブ法

Differences in forming circuit pattern between

(a) Subtractive Technique and (b) Additive Technique

一方,アディティブ法はめっきレジストに沿ってめっきを成長させた後,レジストを剥離してパターンを形成する(図4(b)).そのため,レジストの解像度が良好であれば精度の高いパターン形成が可能である.また,厚いシジストを用いてめっき条件を制御することにより, 厚い銅箔を得ることができる.これにより,低い電気抵抗をもつ回路パターンを形成することができる.

以上のような背景をふまえて,われわれは樹脂フィルムラミネーションにより絶縁層を形成し,アディティブ法により導体回路パターン形成を行うことでビルドアップ配線板の作製,評価を行った.

## 4. ビルドアップ回路パターン作製方法

本開発では,スルーホール付き4層基板をコア基板として用いて,デイジーチェーンパターンを含むテスト基板

図5 ビルドアップ回路パターンの作製プロセス Process flow of build-up circuit pattern

をビルドアップ法で試作した.図5にビルドアップ層の作製プロセスを示す.コア基板に樹脂フィルム(50 μm)をラミネートして絶縁層を形成した.レーザによるビアホール(穴径 表面:100 μm,底:80 μm)形成,デスミア後,スパッタ法によりシード層形成を行った.フォトレジストをラミネートし,フォトマスク越しに露光,現像することによりレジストパターンを形成した.電解銅めっきをほどこした後,レジストとシード層を除去して導体回路パターンを形成した.なお,本法はシード層除去の工程が含まれるため,正確にはセミアディティブ法である.また,サブトラクティブ法による試作も行い,アディティブ法によるものとの比較検討を行った.

#### 5.ビルドアップ回路パターンの評価

## 5.1 ファイン回路パターン形成

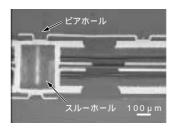

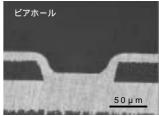

図6に作製したテスト基板の断面写真を示す.ビアホールにほどこした銅めっきによりコア層との電気的な導通が確保できていることがわかる.図7にライン/スペース (L/S) が25/25  $\mu$  mの回路パターンのSEM写真と断面写真を示す.サブトラクティブ法により形成したパターンでは,ライン上部にいくにつれてライン幅が狭くなっており,断面の形状が台形になっていることがわかる(図7 (a)(b)).これは,パターン形成時にアンダーカットが

図6 テスト基板の断面 Cross section of test board with through hole and via daisy chain pattern

図7 回路パターン(L/S=25/25μm)の表面と断面 (a)(b) サブトラクティブ法,(c)(d) アディティブ法 SEM micrographs and cross section of fine pattern (L/S=25/25μm) produced by (a≬b) Subtractive Technique and (c≬d) Additive Technique

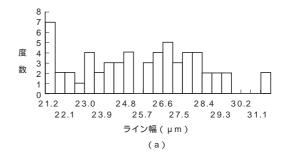

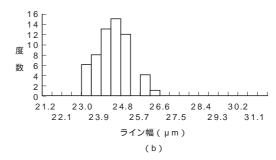

図8 回路パターン(L/S=25/25 μm)のライン幅分布 (a) サブトラクティブ法(b)アディティブ法 Line width distribution of fine pattern (L/S = 25/25 μm) produced by (a) Subtractive Technique and (b) Additive Technique

図9 リフロー試験後の抵抗値 銅箔厚( )9μm( )32μm Resistance of via daisy chain pattern after heat treatment at 260 for 10s Cu plating thickness( )9μm( )32μm

生じたためと考えられる.アディティブ法で作製したものでは,パターン断面の形状が長方形であることがわかる(図7(c)(d)).

図8に回路パターン(L/S =  $25/25\,\mu\,m$ )のライン幅分布を示す.サブトラクティブ法により形成したパターンのライン幅は広い領域( $20\sim30\,\mu\,m$ )に分布を示し,ライン幅のばらつきがみられた(図8(a)).一方,アディティブ法で作製したものでは $25\,\mu\,m$ 付近に狭い分布を示したことから,精度の高いパターンが形成できたことがわかる(図8(b)).

以上のことから,サブトラクティブ法では形成が困難であったL/S = 25/25 µ mの回路パターンは,アディティブ法により問題なく形成できたことがわかる.本開発においてもアディティブ法がファイン回路パターン形成に有効な手法であることが確認できた.

#### 5.2 回路抵抗の耐熱性

ビアを含む回路パターンの耐熱性を評価するためにリフロー試験を行った.評価回路は6ビアデイジーチェーンパターンを用い,加熱プロファイルには,鉛フリーはんだによる実装を想定して,260 で10秒間の加熱を6サイクル行った.また,めっき銅箔が厚い回路(32 µ m)も

作製し、薄いもの(9µm)と比較した、リフロー試験終了後におけるデイジーチェーンパターンの抵抗値を図9に示す、リフロー前の抵抗値は銅箔が厚い回路で0.035 、薄いもので0.096 であり、およそめっき厚に依存していることがわかる、リフロー試験後はサイクル数が増えるにしたがってパターンの抵抗値は上昇した、抵抗値が上昇する原因として樹脂層とめっき間、またはコア基板の銅箔とめっき間における剥離が考えられる、めっきの接続信頼性に関しては今後改善が必要である、

#### 6.む す び

ファイン回路パターンを有するビルドアッププリント配線板の開発をアディティブ法で行った.本法により,サブトラクティブ法では困難であったL/S=25/25 µ mのファインパターン形成が可能になった.今後は高密度配線に対応した多層プリント配線板への応用を視野に入れながら,さらにファインなパターンの形成を検討していく.

リフロー試験によりめっきの接続信頼性が低いことが 示唆された.今後は故障の解析を行い,原因を明らかに した上で改善策を検討していく予定である.

## 参考文献

- 1)中谷ほか:全層IVH構造を有する樹脂多層基板「ALIVH」, 電子材料,10月号,pp. 52-58,1995

- Y. Sato, et al.: A New PCB Utilizing Buried Bump Interconnection Technology (B<sup>2</sup>it), Proc. 7-th Printed Circuit World Convention, pp. P19-1-P19-6, May, 1996

- 3) 伊藤ほか: 銅箔付きポリイミドからなる一括積層のIVH多層配線板,第16回エレクトロニクス実装学術講演大会講演論文集,pp. 31-32,2002

- 4) 中尾ほか: 一括積層ポリイミドIVH多層配線板, フジクラ 技報, 第103号, pp. 48-52, 2002