# セミアディティブ法を適用した全層ポリイミドIVH一括積層配線板

電子デバイス研究所 小野寺 久 美 $^1$ ・板 橋 敦 $^2$ ・南 條 宏 和 $^1$ ・奥 出 聡 $^3$ ・中 尾 知 $^4$

# All Polyimide IVH Co-laminated Multilayer Wiring Board Utilizing Semi-additive Process

K. Onodera, A. Itabashi, H. Nanjo, S. Okude, and O. Nakao

次世代多層配線板に要求される高密度化,薄型化,高速/高周波伝送化に対応すべく,当社ではセミアディティブ法による回路形成を適用した全層ポリイミド IVH 一括積層配線板(Semi-Additive Process applied All Polyimide IVH Co-laminated:SAP-APIC)を開発した。SAP-APIC はセミアディティブ法を採用することで,従来のサブトラクティブ法によるものよりも配線を微細化し,多層板の全層にわたり最小配線幅/スペースで 30  $\mu$  m / 30  $\mu$  m の配線ルールに対応が可能である。本プロセスを適用した6 層配線板を作製して各種信頼性試験を行い,多層配線板に求められる信頼性を満足することを確認した.

We have developed Semi-Additive Process applied All Polyimide IVH Co-laminated (SAP-APIC) multilayer wiring board to cope with strong demands of wiring density growth, thickness reduction and transmission speed increase all which are required for a next-generation multilayer wiring board. Introduction of the semi-additive process enables to realize finer circuit traces in any layer, namely minimum trace width/spacing of 30 microns/ 30 microns, than those by conventional subtractive process and therefore a multilayer board with higher wiring density can be offered. By fabricating 6 layer SAP-APIC boards and performing reliability tests on them, we have confirmed that SAP-APIC satisfies strict reliability requirements for multilayer boards.

### 1. ま え が き

近年、デジタルカメラや携帯電話などの携帯電子機器 の小型化、薄型化、高機能化に伴い、それらに用いられ る配線板にも高密度実装に対応した微細配線、高速化に 対応したインピーダンスコントロールが求められてい る. この流れに対応すべく、片面/両面のフレキシブル プリント配線板 (FPC) においては、エッチングで回路 形成するサブトラクティブ法から、選択的にめっき膜を 成長させ回路形成するセミアディブ法の採用が進んでい る 1) 2). 当社では高密度多層 FPC である全層ポリイミド IVH一括積層配線板 (APIC) を開発しているが、これ はエッチングで回路を形成したFPCを重ね合わせて一 括積層する多層配線板の製造技術である3.今回,セミ アディティブ法で作製したFPCを APIC に適用する検討 を行い、従来の一括積層プロセスをモディファイするこ とで、全層で微細配線可能なセミアディティブAPIC (SAP-APIC) を開発した. これにより、微細配線、イ ンピーダンスコントロールに対応した全層IVH構造の

高密度多層配線板の製品化を実現した.本報では、SAP-APICの開発概要とその信頼性を検証した結果について報告する.

# 2. APIC技術と特長

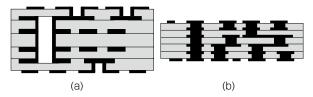

半導体パッケージなど多層構造の微細配線が求められる配線板には、ビルドアップ配線板が採用されている(図 1-a). これは、配線層間接続にめっきスルーホール(TH)を用いた基板をコアとし、その両面に樹脂層・導体層を逐次形成したものである。ビルドアップ配線板は、厚いコアを用いるため、基板全体が厚くなってしまう。さらにはめっきによる銅厚さの増加によって、回路の微細化が制約されるなど、将来の高密度化、薄型化に

図1 多層板構造模式図

(a) ビルドアップ配線板, (b) APIC

Fig. 1. Schematic diagram of substrate.

(a) Build-up substrate. (b) APIC substrate.

<sup>1</sup> マイクロデバイス開発部

<sup>2</sup> マイクロデバイス開発部 (博士)

<sup>3</sup> マイクロデバイス開発部グループ長

<sup>4</sup> マイクロデバイス開発部長

向けた課題が浮上してきた.

一方、APIC(図 1-b)は、多層配線を構成する各層の配線板を個別に作製、層間接着材により各配線板を一括積層して多層化する方法である。配線層間の接続には導電ペーストを用いた埋め込み型ビア(Interstitial via hole、IVH)を採用している。一括積層のプロセスでは、後述するように各配線板を位置合わせ積層した後、全層一括で層間接着と電気的接続を行う。各層の配線形成を並行して進められることでリードタイムを短縮できるとともに、積層前に不良品を排除した後に一括でプレスするため、各工程の不良の累積を低減できる特長がある。また、APICでは各層の回路形成が多層化プロセスと独立しておこなわれるため、多層化プロセスを大幅に変更することなく種々の回路形成法を適用することができる。

# 3. セミアディティブ FPC

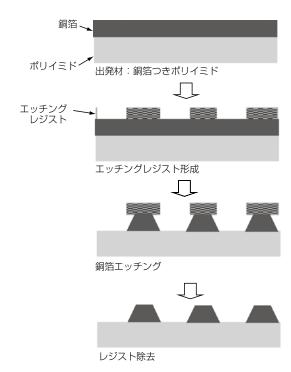

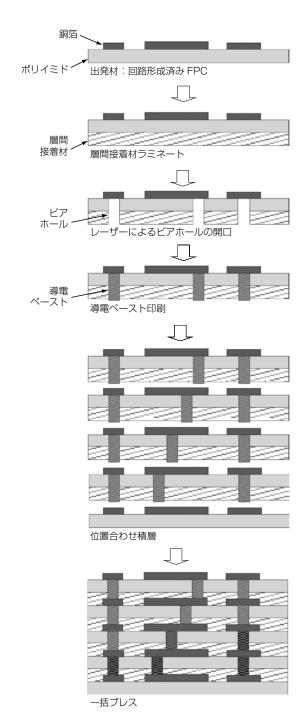

FPCの回路形成には、セミアディティブ法とサブトラクティブ法が用いられている。サブトラクティブ法は、樹脂基板上の銅箔をエッチングレジストでマスクした後、回路以外の銅箔をエッチングし、その後、レジストを除去することで回路を形成する方法である(図 2)、大面積を一括処理可能であり、薬液の管理も比較的容易であるため、広く採用されている回路形成方法であるが、銅のエッチングが厚さ方向だけでなく回路幅方向にも進行するため、回路の断面形状は台形となり、回路幅の厳密な制御や微細な回路形成には限界がある。

一方、セミアディティブ法は電解銅めっきにより必要な部分にのみ回路を積み上げていく方法である(図 3). めっきシード層となる金属薄膜をスパッタなどで被着させたポリイミドフィルム上に、めっきレジストのパターンを形成したのち、電解銅めっきを行って回路で成らとせる。その後、レジストを除去し、次いで回路間のシード層をエッチングすることで配線板が完成する<sup>1)</sup>. セミアディティブ法のめっきはレジスト開口内で厚さ方回路形状が得られる。めっきレジストのフォトリソグラフィの特度で回路幅が決定されるため、高精度で微細な回路形成が可能になる。サブトラクティブ法に比べ回路になるの特度で回路幅が決定されるため、高精度で微細な回路形成が可能になる。サブトラクティブ法はインピーダンスの制御性が良く、高速伝送用途に適した回路形成法であるといえる.

# 4. SAP-APIC基板の作製工程と課題

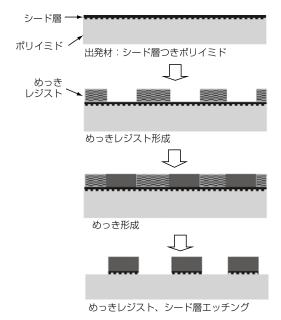

まずAPICの作製工程を図4に沿って説明する. APICの各層を構成する片面/両面FPCを準備する.各層のFPCのポリイミドフィルム上に層間接着材をラミネートし、次いで、レーザー加工によりビアホールを開口する.その後、スクリーン印刷法を用いてビアホール内に導電ペーストを充填する.それらの位置合わせを行 って積層し、加熱プレスすることで、接着材を硬化させ 多層配線板が完成する、導電ペーストは、低温で焼結で きる金属粒子を含み、接着材の硬化と同時にペースト内 の金属粒子が回路の銅と金属結合することで信頼性の高 い層間接続が得られる。

以上のようにAPICでは、導電ペーストと回路との接続信頼性が重要である。サブトラクティブ法で用いている銅張積層板ではレーザー加工したビアホール底面には銅が露出しており導電ペーストと金属結合を形成する。セミアディティブ法を適用した配線板の場合、導電ペー

**図2** サブトラクティブ法の工程 Fig. 2. Subtractive process.

図3 セミアディティブ法の工程 Fig. 3. Semi-additive process.

**図4** APIC工程図 Fig. 4. Process flow of APIC substrate.

ストと接するビアホール底面には、前述したシード層の金属薄膜が存在するため、層間接続へ影響を与えることが懸念される。この影響について実際に基板を試作して調査したところ、シード層と導電ペーストの接合界面には金属結合が生成せず、吸湿リフロー試験や熱衝撃試験を行うことで抵抗値が大きく上昇してしまうなど、接続信頼性に問題があることがわかった。以上の結果から、APIC基板へセミアディティブ法を適用させるために、ビア底のシード層を除去する工程を追加することとした、導電ペーストを充填する前にビア底面のシード層を除去する工程を加えることで、銅とペースト間に金属結合を形成させ、信頼性の高いSAP-APICが実現できる。

表1 APIC 設計ルール例 Table 1. Design rule of APIC substrate.

| セミアディティブ法 | サブトラクティブ法                          |

|-----------|------------------------------------|

| 30 μm     | 50 μm                              |

| 30 μm     | 50 μm                              |

| 250 μm    | 250 μm                             |

| 280 μm    | 300 μm                             |

| 100 μm    | 100 μm                             |

|           | 30 μm<br>30 μm<br>250 μm<br>280 μm |

表2 評価用配線板の仕様 Table 2. Specifications of the test board.

| サイズ         | 10 mm×10 mm   |

|-------------|---------------|

| 層 数         | 6 層           |

| -<br>厚 さ    | 320 μm        |

| 最小配線幅/スペース  | 30 μm/30 μm   |

| パッド径/パッドピッチ | 250 μm/300 μm |

| ビア径         | 100 μm        |

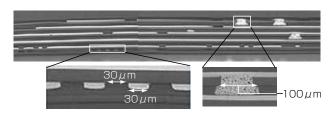

図5 評価用配線板断面 Fig. 5. Cross-section of the test board.

表3 信頼性試験条件 Table 3. Conditions of reliability test.

| 項目       | 条件                                                       |

|----------|----------------------------------------------------------|

| 吸湿リフロー試験 | 125℃/24 hrs⇒ 30℃/60%/192 hrs<br>⇒リフロー(ピーク温度 260℃),連続 3 回 |

| 熱衝撃試験    | -25℃/9 min⇔室温/1 min⇔ 125℃/9 min<br>1000 cycle            |

| 加熱反り試験   | ピーク温度 240℃, シャドウモアレ方式                                    |

SAP-APIC の標準的な設計ルールをサブトラクティブ 法と比較する形で表 1 にまとめた。線幅の微細化に伴い、ビアピッチも微細化できるとともに、多層配線板の全層 にわたり最小配線幅/最小スペース =  $30~\mu$  m/ $30~\mu$  m の配線ルールが採用可能である。

#### 5. SAP-APICの信頼性評価

SAP-APICの評価用 6 層配線板を作製して信頼性試験を行った.評価用配線板(以下サンプル)としてシード層除去を行ったものと,比較用として除去しなかったものを作製した.サンプルの仕様を表 2 に示す.また,サンプルの断面写真を図 5 に示す.信頼性試験として,部品実装用配線板に求められる吸湿リフロー試験,熱衝撃試験,加熱反り試験を実施した.試験条件については

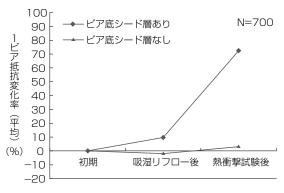

図6 信頼性試験結果 Fig. 6. Results of reliability test.

表 3 にまとめた. 以下, 各試験方法および評価結果について詳述する.

#### 5. 1 吸湿リフロー試験

部品実装用配線板は、部品実装、2 次実装など、複数回のリフロー実装工程を想定した吸湿リフロー耐性が求められる. 試験は、国際規格である JEDEC level 3 に準拠した条件を適用し、試験前後での外観およびビア抵抗値の変化を評価した. 試験後の外観検査では、膨れや剥離など外観上の変化は試験したすべてのサンプルにおいて見られなかった. 試験前後におけるビアの抵抗値の変化をプロットしたグラフを図 6 に示す. ビア底面のシード層を除去しなかったものではビア抵抗に大幅な上昇が見られたものの、除去工程を加えたサンプルでは大幅に改善されていることがわかる. 測定後のサンプルについて断面観察を行い、ビアのクラックや層間剥離がないことを確認した.

#### 5. 2 熱衝撃試験

前処理として上述の吸湿リフロー試験を実施した後に熱衝撃試験を実施した. 1000 cycle の熱衝撃試験前後におけるビアの抵抗値を前節と同様に評価し、変化率をプロットした結果を同じく図 6 に示す. 吸湿リフロー試験と同様に、シード層を除去することで試験前後の抵抗変化が抑えられ金属結合によって信頼性の高い接続が得られていることがわかった. 断面観察による結果でも、層間剥離等の不良の発生は無く、信頼性の高い接続ができていることを確認できた.

# 5.3 加熱反り試験

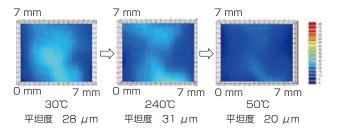

部品実装の工程では、はんだリフロー時に高温に加熱 されるため、構成材料の熱膨張差に起因して配線板が反 ることが懸念される。高温時の平坦性の挙動を調べるた

図7 評価用配線板(7 mm×7 mm)の平坦性 Fig. 7. Coplanarity of test board.

め、加熱反り試験を実施した。シャドウモアレ式の平坦度測定装置を用いて 7 mm角の部品実装範囲内での反り量を測定した。図 7 に示す平坦度測定結果から、上記範囲の反り量は常温時で  $28~\mu$  m、240<sup> $\mathbb{C}$ </sup> 加熱時においても最大  $31~\mu$  mであり、リフロー中に極端な変形を生じないことが確認できた。配線板の反りは層構造の対称性が影響していると考えており、厚さ方向に単純な周期構造を持つ APIC は層構造の対称性が高いため、急激な温度変化にさらされても良好な平坦性を維持できたものと推定される。

# 6. む す び

セミアディティブ法による回路形成を適用したポリイミド多層板(SAP-APIC)の開発を行った. サブトラクティブ法のAPIC製造工程に, ビアホール底面のシード層除去工程を追加することで, 従来のAPICと同等の高い信頼性が得られることを確認した. 作製したSAP-APICは, JEDEC level 3 の吸湿リフローや熱衝撃試験をクリアし, また, 加熱時の平坦性も良好であった. 今後, 高密度化, 高速/高周波伝送化が要求される次世代多層配線板での実用化を進めるとともに, 高い信頼性を要求される半導体パッケージ基板としての応用も期待される.

# 参考文献

- 1) 池田ほか:「微細回路形成技術」, フジクラ技報, 115号, pp.38-41, 2008

- 2) 佐々木ほか:「微細両面FPC」, フジクラ技報, 第107 号, pp.48-51, 2004

- 3) 藤浪ほか:「薄型パッケージ用ポリイミドー括積層基板」, フジクラ技報, 112号, pp.28-32, 2004