# ボール搭載法によるWLPのはんだバンプ形成

電子デバイス研究所 井 上 俊 明1・鈴 木 孝 直2 プリント回路事業部 飯 塚 祐 一3

Solder Bumping by Sphere-Mounting Method for Wafer-Level Package

T. Inoue, T. Suzuki & Y. Iizuka

ウエハレベルパッケージ(Wafer-Level Package; WLP)は軽薄短小化に対応できることから携帯電話をはじめとするモバイル機器に採用されるようになってきた.本研究では,さらなる高信頼化によるWLPの用途拡大を目的として,WLPのはんだバンプをボール搭載法にて形成し,その熱疲労寿命を評価した.

Wafer-Level Package (WLP) has been applied to hand-held mobile devices including cell phones due to its small form factor. In this study, we have formed larger solder bumps for WLP by preformed sphere-mounting method to improve solder joint reliability and have evaluated thermal fatigue life to further broaden the WLP applications.

### 1.まえがき

ユビキタス時代のモバイル機器に使用される電子デバイスには軽薄短小化が求められ,半導体パッケージの形態も小型化,薄型化が急速に進んでいる.表面実装タイプのQuad Flat Package (QFP)やThin Small Out-line Package (TSOP)などからさらに実装面積を減らしたBall Grid Array (BGA)へと移行しており,なかでもWafer-Level Package (WLP)は実装面積を最小にできるという点で注目され,採用が進んでいる.しかしながら,外部リードもインターポーザも有しないWLPは,シリコン製ICチップと実装基板との熱膨張係数の違いによって生じる応力を緩和する事が難しく,両者を接続しているはんだバンプの形状がその実装後の信頼性に大きな影響をおよぼす .13233)

ウエハの電極上に超小型のはんだボールを直接搭載するボール搭載法は、形状のそろった高いバンプを形成できることが特徴である。バンプ高さを高くするとICチップと実装基板との距離を離すことができ、はんだバンプにかかる応力を軽減することができるため、基板実装後の信頼性の向上が期待できる。そこで、ウエハ上に一括してボール搭載しバンプを形成する技術を導入して、実装後におけるバンプ接続部の信頼性を評価したので報告する。

WLPのはんだバンプ形成方法にはめっき法、ペースト印刷法、ボール搭載法の3つがある.表1にそれぞれの特徴を示す.めっき法は電極上に電解めっきによってバンプ材料を析出させる方法であり、フォトリソグラフィーを利用できるために微細なバンプを形成する場合には有利な方法である半面、成分調整が難しく鉛フリーはんだ材料の選択性に制限がある.またスループットが低いために高いバンプを形成することには適さない.ペースト印刷法は、はんだペーストを電極上に印刷しリフロによってバンプにする方法で、安価でスループットが高い特徴があり、当社のWLPにも採用されている.欠点として、バンプ高さのばらつきを抑えることが難しく、またバンプ内にボイドができやすいという課題がある.

これらに対して,ボール搭載法はあらかじめ球状に成 形された超小型のはんだボールを電極上に直接搭載しリ

表1 バンプ形成方法の特徴 Table 1. Feature of bumping method.

| 項目          | ボール搭載法 | ペースト印刷法 | めっき法 |

|-------------|--------|---------|------|

| バンプ高さ       |        |         |      |

| コプラナリティ     |        |         |      |

| <br>バンプ内ボイド |        |         |      |

| ファインピッチ化    |        |         |      |

| 鉛フリー化       |        |         |      |

| 設備投資        |        |         |      |

| スループット      |        |         |      |

| 材料コスト       |        |         |      |

<sup>2.</sup> はんだバンプ形成技術

<sup>1</sup> マイクロデバイス開発部

<sup>2</sup> マイクロデバイス開発部グループ長

<sup>3</sup> ウエハレベルパッケージ部主査

フロによってバンプにする方法であり、はんだペーストよりも電極一か所あたりの金属量を多くすることができるため、ペースト印刷法よりバンプを高くできる.また、はんだボールの寸法を一定に管理する事によりバンプ高さのばらつきを小さくすることができる.しかしながら、スループットを向上させるためにはウエハ全面に一括してはんだボールを搭載する必要があり、例えば8インチウエハに0.5 mmピッチでバンプを形成する場合の搭載ボール数は十万以上となるため、歩留まりの向上には工夫が必要である.

## 3.ボール搭載法によるはんだバンプ形成

#### 3.1 バンプ形成プロセス

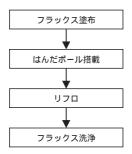

バンプ形成の工程を図1に示す.

まず、ウエハの電極上にフラックスを塗布した.このフラックスは電極表面およびはんだボール表面の酸化物を除去して活性化させるとともに、その粘着力により搭載されたボールを仮固定する役割がある.フラックスはリフロ時に軟化して流動するため、塗布量が多いとはんだボールが移動し隣接したボール同士が結合して図2(a)に示すようにブリッジを形成する可能性がある.逆に塗布量が少ないと電極表面およびはんだボール表面を十分に活性化する事ができず、図2(b)に示すようにバンプを形成できなくなる.そこで、適量のフラックスをウエハ全面に均一に塗布できるようフラックスの粘度やチクソ比を改善するとともに、はんだの濡れ性を向上させるために活性力を強化した.

次に,ウエハ上の電極に対応した位置に貫通穴を設けたボール配列板にはんだボールを吸引し.フラックスが

**図**1 ボール搭載法のプロセスフロー Fig. 1. Process flow of sphere solder mounting.

**図**2 はんだバンプの外観異常 Fig. 2. Abnormal appearance of solder bump.

塗布されたウエハの電極上に位置合わせしてはんだボールを搭載した.はんだボールの吸引時および搭載時に画像処理による検査を行い,さらにボール配列板への吸着条件およびウエハへの搭載条件を最適化することで,本工程の歩留まり向上をはかった.

はんだボールを搭載したウエハを窒素雰囲気中でリフロすることで、はんだボールは溶融しバンプ形状となる、リフロ時のフラックスの流動を抑制するため、リフロープロファイルの温度および時間を最適化した.なかでも昇温速度はバンプ形成に大きな影響をおよぼすため重要な管理項目である.たとえば、昇温速度が大きいとフラックスに含まれる溶剤が急激に気化するためボールが動きやすく、バンプのブリッジが起きる可能性が高くなる.逆に、小さいとウエハの電極やはんだが高温にさらされる時間が長くなるために酸化が進み、はんだが濡れずバンプが形成できなくなる.

フラックスはリフロ後に残渣を残すことなく洗浄しなければならない.そのため,洗浄液に対するフラックスの溶解性を高めるとともに,リフロ時の熱によるフラックスの劣化を抑制するよう耐熱性を向上させた.

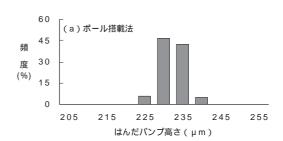

#### 3.2 バンプ高さ

図3に,直径が 0.30 mmのはんだボールを0.50 mmピッチで搭載して形成したバンプとペースト印刷法で形成したバンプの,高さと頻度との関係を示す.前者は後者に対して約1.5倍の高さを持ち,そのばらつきも3 < 10 μmと小さかった.また,ボール搭載法によるバンプ形成工程での不良率は数十ppm以下を達成した.

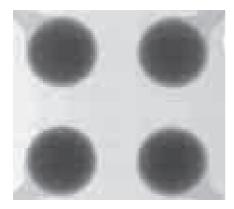

### 3.3 バンプ内ボイド

図4にボール搭載法で形成したはんだバンプのX線透過像を示す.写真からはボイドが確認できなかった.評価精度を考慮すると,バンプ内には少なくとも10 μmを上回るボイドは存在しないことがわかった.

図3 はんだバンプの高さ分布 Fig. 3. Histogram of solder bump height.

**図**4 はんだバンプのX線透過像 Fig. 4. X-ray image of solder bump.

## 4. 実装後信頼性の評価

### 4.1 評価方法

作製したWLPの実装後信頼性の評価として個片化後の チップを基板に実装し,温度サイクル試験を行った.チッ プの外形サイズは4.2 mm角で,49個のはんだバンプが 0.50 mm ピッチでフルアレイ配置されている. 比較のた め,ボール搭載法およびペースト印刷法のそれぞれの方 法をもちいてはんだバンプを形成したチップを用意した. はんだの組成はいずれもSn-3.0Ag-0.5Cuである. 基板は 厚さ0.8 mmのFR-4で,はんだペーストを塗布した電極上 に吸湿処理を施したチップを搭載後,窒素雰囲気中でリ フロして実装した、なおアンダーフィルは使用しなかっ た. すべてのはんだバンプはチップと基板との間のデイ ジーチェーンで直列に接続されており,電気抵抗を連続 的に測定する事ではんだバンプの故障を検出できるよう にした.試験は25 /10分 125 /10分を1サイクルとし. デイジーチェーンの電気抵抗値が10%上昇した時点で故 障と判断した.

#### 4.2 評価結果と考察

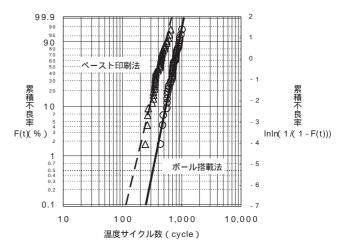

図5に温度サイクル試験で故障した試料についてのワイブル解析の結果を示す.ボール搭載法でバンプ形成したWLPチップについても,ペースト印刷法でバンプ形成したWLPチップについても1次近似に対して良い相関を示しており,いずれも単一の故障モードである事が示唆されている.さらに累積故障率0.1%で比較すると,前者の方が後者に比べて2倍以上長寿命であることがわかる.

## 4.3 故障モードの解析

温度サイクル試験では、故障個所はいずれのサンプルもすべてはんだバンプの接続部付近での破断であり、その他の個所での破断や剥離は発生していなかった.これはワイブルプロットの結果と一致する.また、WLP実装後の熱サイクルでは、最も応力が集中する場所ははんだバンプの接続部付近である事が知られており、()44\5)これを裏付ける結果でもあった.

図5 温度サイクル試験結果のワイブルプロット Fig. 5. Weibull plot of thermal cycle data.

## 5.む す び

WLPの実装後信頼性を向上させるため,ボール搭載法によるはんだバンプ形成技術を確立した.本技術により従来のペースト印刷法によるものよりも形状のそろった高いはんだバンプを形成できるようになり,WLPの長寿命化が可能である事を確認した.

本技術は既に数多くの製品に採用され,量産を行っている.バンプ形成技術としてペースト印刷法に加えボール搭載法を確立したことで,顧客のニーズに合わせたさまざまなソリューションを提供できるようになった.

## 参考文献

- Hong Yang, et al.: Reliability Characterization in Ultra CSP Package Development, IEEE Electronic Components and Technology Conference, 2000, pp.1376-1382

- Lei L. Mercado, et al.: Impact of Solder Pad Size on Solder Joint Reliability in Flip Chip PBGA Packages, IEEE Transactions on Advanced Packaging, Vol.23, No.3, 2000

- 野上ほか: Fine Pitch FBGAの実装技術, エレクトロニクス実装学会誌, Vol.4, No.1, pp.63-67, 2001

- 4) 荘司ほか:熱サイクル負荷を受けるSn-Ag系Pbフリーは んだ接合部の破断寿命評価、エレクトロニクス実装学会誌、 Vol.4, No.4, pp.289-292, 2001

- 風間ほか:低コスト・高信頼ウエハプロセスパッケージ "WPP-2"の開発,エレクトロニクス実装学会誌,Vol.5, No.3,pp.264-271,2002